# Reversible Denial-of-Service by Locking Gates Insertion for IP Cores Design Protection

Brice Colombier\*, Lilian Bossuet\*, David Hély+

\*Laboratoire Hubert Curien Université Jean Monnet Saint-Étienne — France

+LCIS

Grenoble Institute of Technology

Valence — France

## Design-and-reuse paradigm

#### **Problem**

The designer cannot control **how many times** the IP is instantiated.

- Overusing,

- Illegal cloning.

#### One solution

Make the IP unusable unless it has been previously activated.

$\Rightarrow$  Illegal copies are useless.

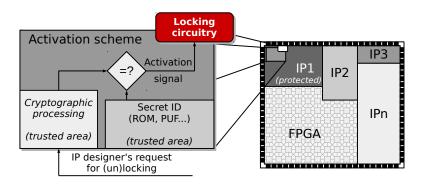

#### Protection scheme architecture

#### Each has its role:

**Security**: relies on a **cryptographic primitive**.

**Uniqueness**: ID, NVM, PUF...

**Disabling**: specific masking/locking module.

# Locking

- FSM,

- Clock,

- Logic.

## Logic masking

In 2008, Roy et al.<sup>1</sup> proposed to **randomly** insert XOR/XNOR gates in the netlist.

<sup>&</sup>lt;sup>1</sup>Roy, Koushanfar, Markov EPIC: Ending Piracy of Integrated Circuits

Design, Automation and Test in Europe, 2008

## Logic masking

In 2013, Rajendran et al.<sup>2</sup> improved the **node selection** method.

# Fault analysis-based node selection

- Requires a fault simulator,

- Computationally expensive.

<sup>&</sup>lt;sup>2</sup>Rajendran, Zhang, Rose, Pino, Sinanoglu, Karri Fault analysis-based logic encryption IEEE Transactions on Computers, 2013

<sup>&</sup>lt;sup>3</sup> Plaza, Markov Protecting Integrated Circuits from Piracy with Test-aware Logic Locking International Conference on Computer Aided Design, 2014

## Logic masking

In 2013, Rajendran et al.<sup>2</sup> improved the **node selection** method.

# Fault analysis-based node selection

- Requires a fault simulator,

- Computationally expensive.

# Security flaw

There is a **gradient** towards the correct key.

A **hill climbing** attack<sup>3</sup> can be mounted:

Choose a random key, flip bits **one after the other** to gradually reduce *HD*(*output*, *test vectors*) to 0.

Link between key bits and masked outputs is too obvious.

<sup>&</sup>lt;sup>2</sup>Rajendran, Zhang, Rose, Pino, Sinanoglu, Karri Fault analysis-based logic encryption IEEE Transactions on Computers, 2013

<sup>&</sup>lt;sup>3</sup> Plaza, Markov Protecting Integrated Circuits from Piracy with Test-aware Logic Locking International Conference on Computer Aided Design, 2014

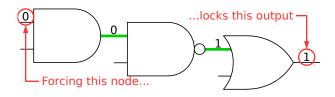

# **Principle**

Propagating a **locking value** through a sequence of netlist's nodes. Forcing an internal node in the netlist **locks a primary output**.

#### **Condition**

For all the nodes in the sequence (green nodes):

They are **forced** to a logic value that **locks** the following logic gate.

#### Which node should be forced?

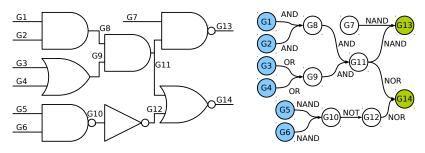

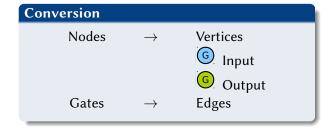

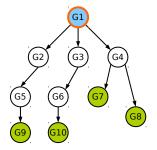

1st step: Build a graph from the netlist.

# **Graph labelling**

**2nd step:** Label vertices with  $V_{forced}$  and  $V_{locks}$  values.

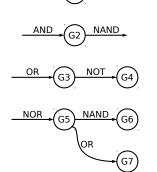

# Labelling

AND

- $V_{forced}$  depends on the **preceding** logic gate.

- $V_{locks}$  depends on the **following** logic gate.

| Node | $V_{forced}$ | V <sub>locks</sub>   |

|------|--------------|----------------------|

| G1   | 0            | 1                    |

| G2   | 0            | 0                    |

| G3   | 1            | $\sim V_{locks}(G4)$ |

| G5   | 0            | {0, 1}               |

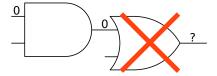

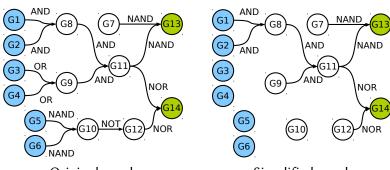

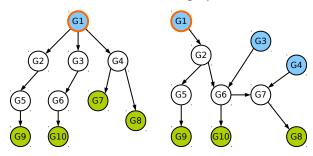

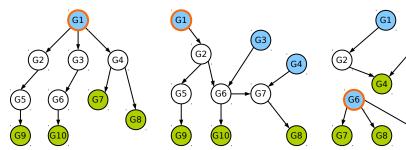

## **Graph simplification**

**3rd step:** Delete **incoming edges** of nodes for which  $V_{forced} \notin V_{locks}$ . Those nodes **cannot propagate** the locking value.

Original graph

Simplified graph

## **Graph cleaning**

4th step: Delete connected components that contain no output.

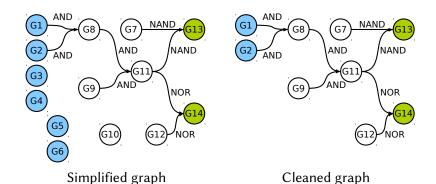

### **Nodes selection**

In the disconnected final graph, which nodes should be locked?

One source vertex

Select the source vertex.

#### **Nodes selection**

In the disconnected final graph, which nodes should be locked?

One source vertex

Multiple source vertices

Select the source vertex.

Select the furthest node spanning all the outputs.

#### **Nodes selection**

In the disconnected final graph, which nodes should be locked?

One source vertex

Multiple source vertices

Multiple source vertices not all outputs spanned

Select the source vertex.

Select the furthest node spanning all the outputs.

Sort the nodes w.r.t to the number of outputs they span and select them greedily.

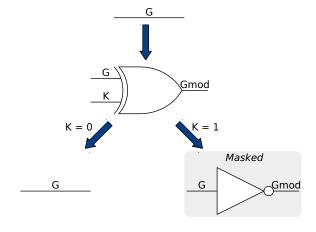

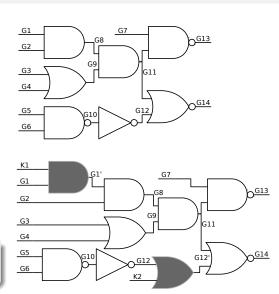

## Locking gates insertion

#### So far, we have:

- list of nodes to lock,

- associated  $V_{locks}$  values.

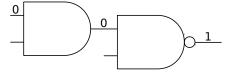

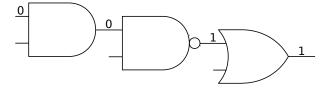

$V_{locks} = 0$ : add AND gate  $V_{locks} = 1$ : add OR gate

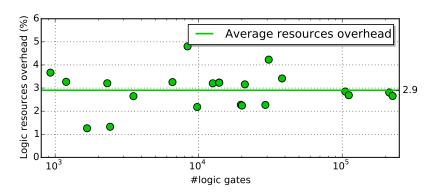

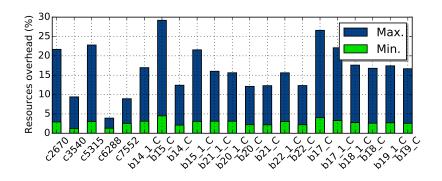

#### Area overhead

**Overhead metric:** percentage of locking gates to add. Implemented on ITC'99 benchmarks (1k to 225k logic gates)

$\sim$ 2x lower overhead than logic masking<sup>2</sup> (+5.7%)

<sup>&</sup>lt;sup>2</sup> Rajendran, Zhang, Rose, Pino, Sinanoglu, Karri Fault analysis-based logic encryption IEEE Transactions on Computers, 2013

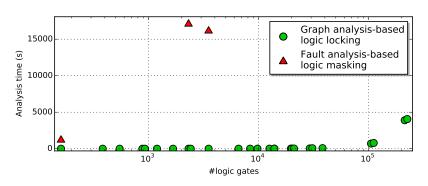

# Analysis time

| Benchmark | #logic<br>gates | Fault analysis-based logic masking <sup>2</sup> | Graph analysis-based<br>logic locking |

|-----------|-----------------|-------------------------------------------------|---------------------------------------|

| c432      | 160             | 20min                                           | 0.03s                                 |

| c7552     | 3512            | 4h30min                                         | 0.87s                                 |

| b19_C     | 225k            | X                                               | 1h15min                               |

<sup>&</sup>lt;sup>2</sup> Rajendran, Zhang, Rose, Pino, Sinanoglu, Karri Fault analysis-based logic encryption IEEE Transactions on Computers, 2013

## Security margin

In the final graph, all nodes are available for logic locking.

**More nodes** can be forced to increase locking strength. It can make hill-climbing attack and reverse-engineering **harder**. The designer **tunes** the resources overhead/locking strength **ratio**.

#### Conclusion

## **Key points:**

- Logic locking is a **powerful** way to make the circuit **unusable**:

- Very low overhead,

- Tunable security margin.

- Graph analysis-based selection method:

- Computationally efficient,

- Simple **EDA integration**.

- Logic masking/locking alone is not secure,

- A **cryptographic primitive** is necessary for security.

Presented at ISVLSI 20154.

All Python scripts are available on the SALWARE project webpage<sup>5</sup>.

<sup>&</sup>lt;sup>4</sup> Colombier, Bossuet, Hély Reversible Denial-of-Service by Locking Gates Insertion for IP Cores Design Protection IEEE Computer Society Annual Symposium on VLSI, 2015

<sup>&</sup>lt;sup>5</sup>http://www.univ-st-etienne.fr/salware/FOGP.html

#### Conclusion

# Questions

Contact: b.colombier@univ-st-etienne.fr